# BLOCK I: INSTRUCTION SET ARCHITECTURE AND PROCESSOR DESIGN

Unit 1: Instruction Set Design and Architecture Unit 2: Combinational Circuit and its Applications

Unit 3: Computer Arithmetic

Unit 4: Register Transfer Language and Processor Logic

Design

# UNIT 1:INSTRUCTION SET DESIGN AND ARCHITECTURE

#### **Space for learners:**

#### **Unit Structure:**

- 1.1 Introduction

- 1.2 UnitObjectives

- 1.3 Instruction Set Design

- 1.3.1. How many addresses

- 1.3.1.1. 3-address machines

- 1.3.1.2. 2-address machines

- 1.3.1.3. 1-address machines

- 1.3.1.4. 0-address machines

- 1.3.2. Types of Instructions

- 1.3.2.1. Data Transfer Instructions

- 1.3.2.2. Arithmetic Instructions

- 1.3.2.3. Bit Manipulation Instructions

- 1.3.2.4. Program Execution Transfer Instructions

- 1.3.2.5. Processor Control Instructions

- 1.3.2.6. Iteration Control Instructions

- 1.3.2.7. Interrupt Instructions

- 1.4. Addressing Modes

- 1.4.1. Immediate Addressing

- 1.4.2. Direct Addressing

- 1.4.3. Indirect Addressing

- 1.4.4. Register Addressing

- 1.4.5. Register indirect Addressing

- 1.4.6. Displacement Addressing

- 1.4.7. Stack Addressing

- 1.5. Processor Organisation

- 1.6. Register Organisation

- 1.6.1. User visible registers

- 1.6.2. Control and status registers

- 1.7. Instruction Cycle

- 1.7.1. The Indirect Cycle

- 1.7.2. Data Flow

- 1.8. Data Representation

- 1.8.1. Number Representation

- 1.8.1.1. Complements

- 1.8.2. Fixed point representation

- 1.8.3. Floating point representation

#### 1.8.4. Character representation

- 1.9. Summing up

- 1.10. Answers to Check Your Progress

- 1.11. Possible Questions

- 1.12. References and Suggested Readings

#### 1.1 INTRODUCTION

In this unit, we will discuss addressing types, addressing modes and representation of characters. The organization of computer processor as well as various registers is explained in brief. Here, machine language program using different addressing type is elaborated. We will also know about the instruction cycle. At the end of the chapter integer, fixed point representation, floating point representation and character representation inside computer are discussed.

### 1.2 UNIT OBJECTIVES

The objectives of the unit are:

- To know the addressing type

- To know the addressing mode

- Overview of processor

- Overview of registers

- To know about instruction cycle

- Data representation in computer

#### 1. 3 INSTRUCTION SET DESIGN

An instruction set is a collection of machine language or assembly language instructions that are understood by central processing unit (CPU). The following issues are considered in instruction set design:

Whether operands are to be stored in registers, memory, stack or accumulator

- How many operands are present in instructions 0, 1, 2, or

3

- Whether access modes of operands are register, immediate, indirect and so on.

- What are the operations that are supported in instruction add, sub, mul etc.

# 1.3.1 How many addresses

Let us assume the statement in a high level programming language given bellow

$$a = a + b + a * c$$

It is clear that the value of a multiply with c is added with a, b and the final result is stored in the variable a. You know the precedence and associativity rules of high level languages. However, you cannot expect the computer hardware to directly understand these rules.

It requires operations to be performed in small steps. The desired result will be produced after going through **sequence of simple steps**. Hence, it eliminates the necessity for the machine to understand about these rules. In most of the cases operands name i.e. **address** is used rather than value. The machine may be following types depending on addresses:

- 3-address machines

- 2-address machines

- 1-address machines

- 0-address machines

Here number 0, 1, 2, 3 indicates maximum number of address/operand the machine can have.

Here we will use the convention that 'first operand is destination' in an instruction. This means we will consider that the result of operation will be stored in first operand of the instruction.

#### STEP TO CONSIDER

The address may be either memory or computer registers. In a particular machine final result of operation may be stored in first, or last operand. Here, we consider that the first operand will hold the result of the operation.

#### 1.3.1.1 3-address machines

The general format of a 3-address machine instruction is:

Operation dst, op1, op2

Here, *operation* indicates opcode of the operation to be performed, the first operand *dst* represent destination operand i.e. where the result of operation will be stored, op1 and op2 indicates two source operands between which operation is to be performed. Thus the following instruction means:

ADD R2, R1, R0

Add the values stored in register R1 and R0, and store result in the register R2.

When all operands of instructions are only in register then we call it a **register-register** machine or a **load-store** machine. Instead of that if all operands of instructions are only in memory then we call it a **memory-memory** machine. The following is such an example:

ADD X, Y, Z

Add the value of variable y to the value of variable z and then store the result in the memory location x. In a memory-memory machine the CPU has to get the operands from memory prior to execution of the operation. After that it has to store the result back in memory. There are several ways to specify the address of an operand. We will discuss this topic in addressing mode section.

Let us now see how to implement a 3-address instruction for the statement

```

a = a + b + a * c

```

Answer:

MUL R4, a, c # store a\*c in R4

ADD R1, a, b # store a + b in R1

ADD R1, R1, R4 # Store result in R1

The final result of the expression can be found in register R1.

#### 1.3.1.2 2-address machines

The general format of 2-address machine instruction is:

Operation dst, op

where, *operation* is opcode of the operation, *dst* represent the source operand as well as destination, *op* represent the second source operand. Let us see the following instruction

#### ADD R1, R2

*The* meaning of this instruction is to add the values stored in registers R1 and R2, and then store the result back in register R1.

The advantage of 2-address instructions over three-address instructions is that it helps in preserving memory, since they are shorter. More over shorter instructions take less time for fetching. The drawback having two-address instructions is that one of the source operands is destroyed. It requires extra moves *to retain the operand* as sometimes operand may be needed later.

Let us now see how to implement a 2-address instruction for the statement

```

a = a + b + a * c

```

#### Answer:

MUL c, a# multiply a, c and store in cMOV R1,c# move content of c to R1ADD b,a# add a, b and store in bMOV R2,b# move content of b to R2ADD R1, R2#add R1, R2 and store in R1

The final result of the expression can be found in register R1.

#### 1.3.1.3 1-address machines

In a 1-address machine accumulator has a source operand and result of operation is put back implicitly in the accumulator. The instruction needs to indicate the second source operand. The format of a 1-address instruction is as follows:

#### operation op

The opcode 'operation' is the name of the operation to be done, op indicates either source or destination operand. Here the instruction:

#### ADD a

It means addition of value of variable a with the content of accumulator. The result of addition is put in the accumulator. The accumulator is a special purpose register.

Let us now see how to implement a 1-address instruction for the statement.

$$a = a + b + a * c$$

#### Answer:

| LOAD a | # load content of $a$ in accumulator    |

|--------|-----------------------------------------|

| MUL c  | # multiply accumulator i.e. $a$ and $c$ |

| ADD b  | # add b to previous contents of the     |

|        | accumulator i.e. $a * c + b$            |

| ADD a  | # a * c + b + a                         |

| STO a  | # store the final result in location a  |

The final result of the expression can be found in the memory location a.

#### STOP TO CONSIDER

As the number of addresses reduced the number of instructions increases to do the same task.

#### 1.3.1.4 Zero-address machines

The zero-address machines are implemented using stack. A stack is last in first out (LIFO) data structure that is operated by using PUSH and POP. PUSH moves an operand from computer memory into top of stack, on the other hand POP gets out the last item from top of the stack. Only PUSH and POP indicates an operand. No other opcode specify any operand. This is the reason why it is called a zero address machine. The question is how then operands are handled by the machine for the operation. It is done by

extracting top two elements of stack and putting the result back into stack.

Let us see how to implement a zero-address instruction for the statement

```

a = a + b + a * c

```

#### **Answer:**

```

PUSH a# push the value of aPUSH c# push the value of cMUL# multiply top two value a * cPUSH b# push the value of b;ADD# add top two value b + a * cPUSH a# push the value of aADD# add top two value a + b + a * c

```

POP a # store in top of stack in a

The final result of the expression can be found in the memory location a.

# 1.3.2 Types of Instructions

The computer supports the following types of instructions:

- Data Transfer Instructions

- Arithmetic Instructions

- Bit Manipulation Instructions

- Program Execution Transfer Instructions

- Processor Control Instructions

- Iteration Control Instructions

- Interrupt Instructions

#### 1.3.2.1 Data Transfer Instructions

These instructions transfer data from the source to the destination location inside the computer. The common data transfers are among registers or between registers and memory or between the register (s) and the input/output devices. Different computer uses various mnemonics for the same instruction. The following are some of the data transfer mnemonics with their meaning.

- MOV: Transfer data from register to resister or resister to memory.

- ST: Store from register (accumulator) to memory

- LD: Load data from memory to register

- PUSH: Transfer data from CPU register to top of the stack.

- **POP:** Transfer data from top of stack to CPU register

- **XCHG:** Exchange data between two given locations.

- IN: Read data from an input port to accumulator.

- **OUT:** Transfer data from accumulator to particular output port.

#### 1.3.2.2 Arithmetic Instructions

The basic arithmetic operations are addition, subtraction, multiplication and division between two numbers. These arithmetic operations are performed between two operands. Some of the arithmetic operations may be performed on a single operand too.

Following a few arithmetic instructions:

- **ADD**: Add the contents of two source locations.

- MUL: Multiply the contents of two source locations.

- **DIV**: Divide content of one source locations with the other.

- **SUB**: Subtract content of one source locations from the other.

- **ADC**: Add the contents of two source locations with carry.

- **INC**: Increment the content of source location by 1.

# 1.3.2.3 Bit Manipulation Instructions

These instructions manipulate data in bit level i.e. operations like shift or logical. Below is a few instructions of this group with meaning are given:

• **NOT**: This invert each bit of source bit pattern.

- **AND**: Logical AND operation between each corresponding bit of both source operand.

- **OR:** Logical OR operation between each corresponding bit of both source operand.

- **XOR** –Perform logical Exclusive-OR operation between each corresponding bit of both source operand.

- SHL: Perform bits shift towards left and fill zero in LSBs.

- SHR: Perform bits shift towards left and fill zero in MSBs.

# 1.3.2.4 Program Execution Transfer Instructions

These instructions transfer the control during an execution of instructions. The transfer of control during execution of instruction may be conditional or unconditional. A few such examples are listed below:

- CALL: It calls a subprogram and saves the return address on top stack.

- **RET:** Returns from subprogram/function to the main program.

- **JMP:** Jumps to the given address and process the next instruction.

- **JC:** Jumps when value of carry flag is 1

- **JNC:** Jumps when value of carry flag is 0

#### 1.3.2.5 Processor Control Instructions

These instructions set or reset the flag values and thus control the actions of the processor. Following are the instructions under this group:

- STC: Set the carry flag (CF) to 1

- **CLC:** Reset the carry flag i.e. CF = 0

- **CMC:** Complement state of carry flag.

- **STI:** Set the interrupt flag to 1.

- **CLI:** Reset the interrupt flag to 0.

# 1.3.2.6 Iteration Control Instructions

These instructions can execute a group of instructions repeatedly. A few list of iteration control instructions are:

- LOOP: Execute a group of instructions repeatedly until the condition is true.

- **JCXZ:** Jump to a given address if CX = 0

# 1.3.2.7 Interrupt Instructions

These instructions call an interrupt during execution of instructions.

- INT: Interrupt the process and call service routine.

- **INTO:** Interrupt the process if OF = 1

- **IRET:** Return to main program from interrupt service.

#### CHECK YOUR PROGRESS-I

| l |                                                                                                                     |

|---|---------------------------------------------------------------------------------------------------------------------|

|   | 1. When all operands of instructions are only in register then we call it a machine.                                |

|   | 2. If all operands of instructions are only in memory then we call it a machine.                                    |

|   | 3. The drawback having two-address instructions is that one of the source operands is                               |

|   | 4. In a one-address machine the result of operation is put back implicitly in the                                   |

|   | 5. The zero-address machines are implemented using                                                                  |

|   | State TRUE or FALSE:                                                                                                |

|   | 6. The processor has three types of organization.                                                                   |

|   | 7. The advantage of two-address instructions over three-address instructions is that it helps in preserving memory. |

|   | 8. The accumulator is a special purpose register.                                                                   |

|   | 9. MOV is control transfer instruction.                                                                             |

|   | 10. POP insert an operand from computer memory into top of stack.                                                   |

#### 1.4 ADDRESSING MODES

In a typical instruction, we see the address fields are relatively small. The purpose of addressing mode is to reference main memory locations as large as possible. This is the reason why a variety of addressing modes have been implemented. The most commonly used addressing modes are:

- Immediate

- Direct

- Indirect

- Register

- Register indirect

- Displacement

- Stack

| Mode         | Algorithm  | Advantage     | Disadvantage    |  |

|--------------|------------|---------------|-----------------|--|

| Immediate    | Operand=A  | No memory     | Limited operand |  |

|              |            | reference     | magnitude       |  |

| Direct       | EA=A       | Simple        | Limited address |  |

|              |            |               | space           |  |

| Indirect     | EA=(A)     | Large         | Multiple memory |  |

|              |            | address place | reference       |  |

| Register     | EA=R       | No memory     | Limited address |  |

|              |            | reference     | space           |  |

| Register     | EA=(R)     | Large         | Extra memory    |  |

| indirect     |            | address place | reference       |  |

| Displacement | EA=A+(R)   | Flexibility   | Complexity      |  |

| Displacement | EA= top of | No memory     | Limited         |  |

|              | stack      | reference     | applicability   |  |

Table 1.1Basic Addressing Modes

The Table 1.1depicts the address calculation procedure for each addressing mode. Each of the addressing modes will be represented with different opcodes. The opcode may be one or more bits in the instruction format.

#### STOP TO CONSIDER

The effective address of operand is calculated after decoding the opcode.

# 1.4.1 Immediate Addressing

The immediate addressing holds the operand value in the instruction.

Operand = A

This addressing mode is generally used to set initial values of variables or constants. The primary advantage is that there is no need of memory reference. Thus it saves one memory or cache cycle in the instruction cycle. The disadvantage of immediate addressing mode is that size of the number is limited to size of the address field.

## 1.4.2 Direct Addressing

In direct addressing mode the address field holds the effective address of the operand:

EA = A

The advantage of direct addressing mode is that it needs only one memory reference. The disadvantage this addressing mode is limited address space accessibility.

# 1.4.3 Indirect Addressing

In direct addressing mode usually length of the address field is less than word length. It causes limitation in address range. If the address field refers to address of a word in memory, it can access a full-length address of the operand. This way of accessing memory word is known as indirect addressing. In indirect addressing mode the address field contains address of another memory location where the value of actual operand remains.

EA = (A)

The parenthesis interpreted as contents of A is another address. The disadvantage of indirect addressing is that it requires two

memory references to fetch actual operand value, first to get its address and next to get its value.

## 1.4.4 Register Addressing

The register addressing mode has similarity to direct addressing. The difference here is that address field indicates a register instead of main memory address:

$$EA = R$$

The register R specifies the address where the operand value contains. The advantages of this mode are that a small address field is needed and no memory references needed means less time required for fetching instruction. The disadvantage of this mode is that the available address space is limited to registers only.

## 1.4.5 Register Indirect Addressing

The register indirect addressing mode is similar to indirect addressing mode. The only difference is that address field refers to a register instead of memory location. Let us see the register indirect address.

$$EA = (R)$$

The advantages and disadvantages of register indirect addressing mode are similar to indirect addressing mode. But, register indirect addressing mode has one more advantage since it uses one less memory reference it saves one cycle time when it is executed.

# 1.4.6 Displacement Addressing

The displacement addressing mode combines the direct addressing with register indirect addressing. The effective address in this mode looks like as:

$$EA = A + (R)$$

This addressing mode the instruction contains two address fields, out of which at least one of it is explicit. The value stored in one of

the addresses field (i.e. A) is used directly. The contents of second address field i.e. register is added to A to obtain the effective address. We will discuss three most commonly used displacement addressing:

- Relative addressing

- Base-register addressing

- Indexing

**RELATIVE ADDRESSING:** The relative addressing is also known as PC-relative addressing. In this mode of addressing the register that implicitly referenced is program counter (PC). As we know PC contains the address next instruction to be executed. Hence, it is added to the address field in order to produce the *EA*. This is how the effective address in this addressing mode is a displacement relative to the address of the instruction.

EA = PC + address field value

**BASE-REGISTER ADDRESSING:** In the base-register addressing mode, the referenced register contains a main memory address. The address field indicates a displacement from that address, which is usually an unsigned integer.

EA=base register + address field value

**INDEXING:** In this addressing mode, the effective address of the operand is calculated by adding content of index register with address field value.

EA = IR + address field value

The indexing mechanism is extensively used for implementing iterative operations. Suppose a list of numbers present in memory location starting from A and we want to add 1 to each number on that list. Here, we have to fetch each number and after adding 1 to it, store it back to that location. The effective addresses that requires are A, A + I, A + 2, . . ., and so on to last location. It can be done easily with indexing. The value of A is stored in the instruction's address field value, and the index

register is initialized to 0. At the end of each operation, index register is incremented by 1.

#### **Space for learners:**

# 1.4.7 Stack Addressing

The stack addressing is also referred to as a *last-in-first-out* or *queue pushdown list*. In this addressing mode items are placed to the top of the stack. Hence, the stack is partially filled at any given time.

The stack is associated with a pointer called stack pointer (SP) whose value refers to the top address of the stack. If the top two item of the stack is in processor registers, the SP references the third item of the stack. The stack pointer is a dedicated special purpose register. It is a form of implied addressing. The instructions do not require a memory reference; it always implicitly indicates the top of the stack.

**CHECK YOUR PROGRESS-II**

# 11. The purpose of addressing mode is to reference as large as possible. 12. The immediate addressing mode generally used to set initial values of or . 13. In direct addressing mode address field holds address of the operand. 14. In indirect addressing mode the address field contains of another memory location. 15. The displacement addressing mode combines the direct addressing with addressing. State TRUE or FALSE: 16. The advantage of direct addressing mode is that it needs only one memory reference. 17. In register addressing mode one memory references needed. 18. The stack is associated with a pointer called stack pointer.

19. Effective address is calculated after decoding an

20. In stack addressing two memory references needed.

instruction.

#### **Space for learners:**

#### 1.5 PROCESSOR ORGANISATION

The computer processor needs to do the following things to execute an instruction:

- **Fetch instruction:** The processor *has* to read instructions from memory i.e. from register, cache or main memory.

- **Interpret instruction:** After reading an instruction it is decoded to know what action to be performed.

- Fetch data: During the execution of an instruction it may need to read data from computer memory or input/output (I/O) module.

- **Process data:** In execution time of an instruction, it may have to perform either arithmetic or logical operation on data.

- Write data: At the end of an instruction execution, the results may need to write data to main memory or an I/O module. In order to do these, it clears that the processors sometimes have to store intermediate data. Hence, the processor requires a small internal memory.

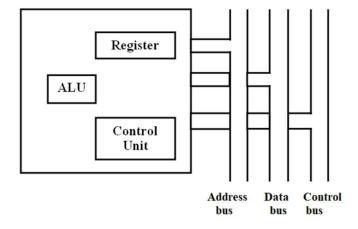

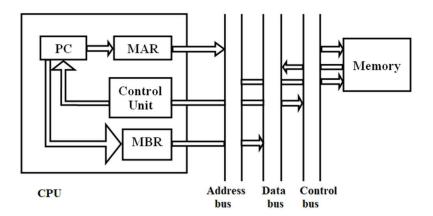

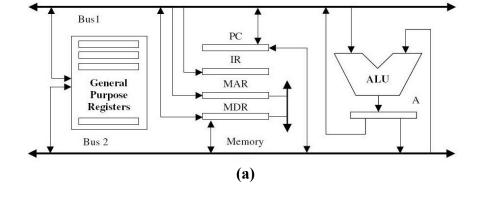

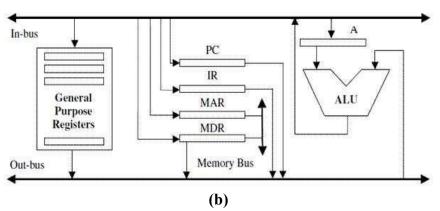

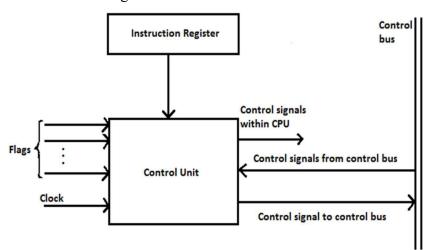

Figure 1.1 is a block diagram of a processor depicting its connection to the rest of the system through system bus. The vital components of the central processing unit are

- Arithmetic and logic unit (ALU)

- Control unit (CU).

- Registers

Figure 1.1: The block diagram of CPU

The ALU performs the actual processing of data. The CU controls the data and instructions movement in the processor. It also controls the operations of the ALU. The figure also depicts internal memory of processor, called registers.

In general, CPU or processor organization has three categories depending on the number of address fields:

- Single Accumulator organization

- General register organization

- Stack organization

In accumulator based organization, a special purpose register called accumulator is used for performing the operations. In general, register organization involves different registers in the computation tasks. In the stack organization the calculations performed on top of the stack. The instruction of stack organization does not contain any address field. In general, a combination of different organizations is mostly used.

#### 1.6 REGISTER ORGANISATION

The computer system consists of memory in different level called hierarchy. At top levels of the hierarchy means memory is faster than the below level. In this level it is smaller as well as more expensive. The register inside the processor is top level memory followed by cache memory and main memory respectively. The registers have two categories:

- User-visible registers

- Control and status registers

#### STOP TO CONSIDER

The address bus, data bus and control bus are together called system bus. Operand address bits can travel through address bus, data bits travel through data bus and CPU generated signal travel through control bus. The processor interaction with main memory is done through these buses.

# 1.6.1 User-Visible Registers

The user-visible registers are used by assembly language programmer in order to minimize main memory references. It can be in the following types:

- General purpose register

- Data

- Address

- Condition codes

General-purpose registers are used to store temporary data during execution of instruction. For a given *opcode* the general-purpose register can hold the operand. This is true use of general-purpose registers. The general-purpose registers sometimes can be used for addressing purpose (e.g., register indirect, displacement).

**Data registers** can be used to hold data only. It cannot be used for calculating of operand address.

**Address registers** may either general purpose or devoted to an individual addressing mode. The following are examples of it:

- **Segment pointers:** The segment register is used to hold the address of the base of the segment.

- **Index registers:** These registers are used for auto indexing in indexed addressing.

- Stack pointer: In stack addressing a dedicated register is used called stack pointer.

**Condition codes** (*flags*): These are bits set by the processor depending on result of an operation. As we know, result of arithmetic operation may be positive, negative, zero, or overflow. In this case a condition code (*flag*) is set and result is stored in memory or register. Subsequently the code may be tested during execution of conditional branch operation.

# 1.6.2 Control and Status Registers

The operations of processor are controlled by variety of internal registers. In general, these registers are not visible to programmer or user. Here, we will discuss four such essential registers.

- **Program counter (PC):** It holds the address of the next instruction to be executed.

- Instruction register (IR): It holds the address of currently executed instruction.

- Memory address registers (MAR): It holds the address of an instruction to be fetched.

- Memory buffer registers (MBR): Holds data that needs the current instruction or result produced by the instruction. Another register that is included in a processor is called the *program status word* (PSW). It contains condition code and other status information. The followings are status flags:

- Sign: It holds sign bit of the recent arithmetic operation.

- Zero: It is set when the result of operation is 0.

- Carry: It is set if addition operation produce a carry or borrow (for subtraction) from lower order bit.

- Equal: Set if a logical comparison of two operands is equal.

- Overflow: When arithmetic operation produces overflow it is set.

- Interrupt Enable/Disable: This flag is used to enable or disable the interrupts.

- **Supervisor:** It indicates the execution mode of processor (supervisor or user). Some of the privileged instructions are executed only in supervisor mode. Similarly, certain memory location can be accessed through supervisor mode only.

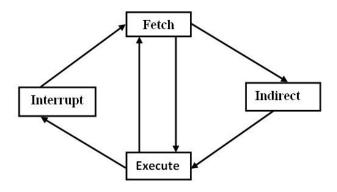

#### 1.7 INSTRUCTION CYCLE

An instruction cycle goes through the following stages: •Fetch: The processor reads the next instruction from PC

- •Execute: Decode the *opcode* and perform the required operation.

- **Interrupt:** If interrupt occurs, pause the current process, save status of it and go to the interrupt.

Before elaborating instruction cycle it's important to know one additional stage called indirect cycle.

# **CHECK YOUR PROGRESS-III** 21. The performs the actual processing of data. 22. The CPU organization has categories. 23. The computer system consists of memory in different level called \_\_\_\_\_. 24. registers are used to store temporary data during execution of instruction. 25. The execution mode of processor either or . State TRUE or FALSE: 26. The CU controls the data and instructions movement in the processor. 27. The segment register is used to hold the address of the base of the segment. 28. PC holds the address of current instruction executing. 29. MBR holds the address of an instruction to be fetched. 30. Carry flag is set if addition operation produces a carry.

# 1.7.1 The Indirect Cycle

During instruction execution it may have one or more operands that need memory access. In case of indirect addressing additional memory accesses are needed. The Figure 1.2 depicts instruction cycle.

After fetching the instruction it is checked to see if it involves any indirect addressing. If indirect addressing involves, the operands are fetched according to indirect addressing. After execution, an interrupt will occur before fetching the next instruction.

Figure 1.2 Instruction Cycle

After fetching the instruction the operand are fetched from memory. If the operand is in register then fetching is not required. Once execution of instruction is completed the result may be needed to store in main memory.

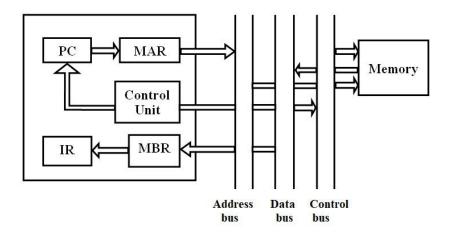

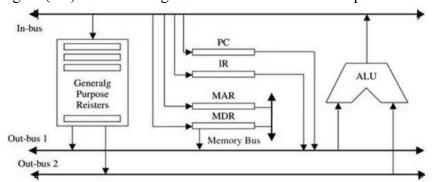

#### 1.7.2 Data Flow

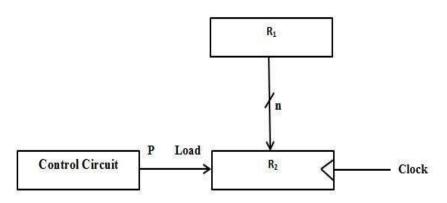

In an instruction cycle sequence of events occurs according to the design of processor. Suppose, a processor consists of a program counter (PC), a memory address register (MAR), a memory buffer register (MBR), and an instruction register (IR).

Figure 1.3 Data Flow, Fetch cycle

Figure 1.3 depicts the data flow during fetch cycle. The PC holds the address of the next instruction to be fetched. This address is placed on the address bus through the MAR.

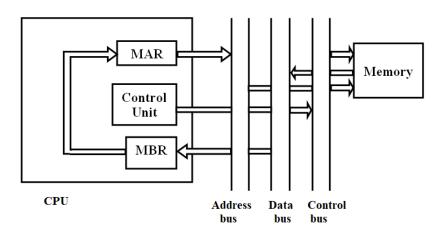

The CU requests a main memory read to fetch the required data for the instruction. The requested result is placed on the data bus and goes to the MBR and finally reached the IR. In the mean time, the PC is incremented for fetching the next instruction. At the end of fetch cycle, the CU checks the IR to know whether it's holding an operand specifier using indirect addressing. If indirect addressing is found, indirect cycle is performed after fetch cycle. Figure 1.4 depicts this simple cycle. The address reference bits of the MBR are transferred to the MAR. After that the CU places a memory read request. Then desired address of the operand is placed in MBR through address bus.

Figure 1.4 Data Flow, Indirect cycle

The fetch and indirect cycles are very simple. The *execute cycle* may have various stages. It many involve ALU operation, register transfer of data, read/write operation from memory or I/O. On the other hand the *interrupt cycle* is as simple as fetch and indirect cycle. It is depicted in figure 1.5. Before going to interrupt, current status of the PC must be in order to resume normal activity after the interrupt. So, the contents of the PC is transferred to the MBR and written to memory. For this purpose special memory location is reserved and it is loaded into the MAR from the CU. The special memory may be a stack pointer. The PC is filled with the address of interrupt routine. Henceforth, the next instruction cycle will fetch the desired instruction.

Figure 1.5 Data Flow, Interrupt Cycle

#### STOP TO CONSIDER

The instruction cycle has different stages fetching, decoding opcode, effective address calculation, execution of operation on data and writing data in memory that are executed in sequence.

#### 1.8 DATA REPRESENTATION

A digital computer represents all types of information in binary number system due to following reasons:

- In digital computers all electronic components operate in binary mode.

- Computers use binary system where only two digits present.

- Whatever can be done using decimal number system can also be done using a binary number system.

## 1.8.1 Number representation

The numbers in computer are represented using binary number system. An r base number system uses r distinct digits. The decimal number has 10 digits. So, decimal numbers are 10-base number system. The binary numbers system has two digits '0' and '1'. It is called base 2 number system. The octal numbers system has eight digits 0, 1, 2, 3, 4, 5, 6 and 7. The decimal number 831.6 can be written as follows with power of base 10.

$$8 \times 10^{2} + 3 \times 10^{1} + 1 \times 10^{0} + 6 \times 10^{-1}$$

When a binary number 101101 is written in this way with power of base 2, it provides decimal equivalent.

#### STOP TO CONSIDER

The hexadecimal numbers system has 16 digits 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E and F.

$$1 \times 2^5 + 0 \times 2^4 + 1 \times 2^3 + 1 \times 2^2 + 0 \times 2^1 + 1 \times 2^0 = 45$$

The decimal number can be converted to r base number system by using the steps:

- At first the number is separated into its integer and fraction parts and then each part converted separately.

- The integer part is converted to r base by dividing it successively with r until it becomes zero.

- The remainders in reverse order give the r base equivalent.

- The fraction part is converted to r base by multiply it repeatedly by r until its fraction part becomes zero.

Suppose, decimal number 112.8125 has to convert into binary. Here integer part is 112 and fraction part is 0.8125. At first, we will convert integer part 112 into binary then fraction part according to above rules. Since binary number system is 2 base we will divide 112 by 2 until it become zero. The following table depicts the process.

| Division     | Remainder |

|--------------|-----------|

| 112 / 2 = 56 | 0         |

| 56 / 2 = 28  | 0         |

| 28 / 2 = 14  | 0         |

| 14 / 2 = 7   | 0         |

| 7 / 2 = 3    | 1         |

| 3 / 2 = 1    | 1         |

| 1 / 2 = 0    | 1         |

Now write down the remainder in reverse order i.e. 1110000 which is binary equivalent number of decimal integer 112. Next, the fraction part 0.81252 is multiplied by 2. The fraction of that result is again multiplied by 2until fraction part become zero.

| Multiplication        | Resultant integer part (R) |

|-----------------------|----------------------------|

| 0.81252 x 2= 1.625    | 1                          |

| 0.6252 x 2= 1.25      | 1                          |

| 0.252 x 2= 0.50       | 0                          |

| $0.50 \times 2 = 1.0$ | 1                          |

| $0 \times 2 = 0$      | 0                          |

The binary equivalent of fraction will be 0.11010. Using the same rules we can convert a decimal number to any base system.

# 1.8.1.1 Complements

Complements simplify the subtraction and logical manipulation in digital computer. There are two types of complements present in r base system namely r's and (r-1)'s complement. If a number N in r base contains n digits, the (r-1)'s complement of N is calculated as  $(r^n-1)-N$ . For a decimal number, the 9's complement of N is  $(10^n-1)-N$ . Thus, 9's complement of 545700 is 999999 -545700=454299. In case of binary number, the 1's complement of N is calculated as  $(2^n-1)-N$ . Thus, 1's complement of 1011000 is 1111111-1011000=0100111. Simply, 1's complement is obtained by just toggling all bits. The r's complement of a number N with n-digit is calculated as n-N. This is like adding 1 to the (r-1)'s complement of the number. Thus, 10's complement of 2389 is 7610 +1=7611. Similarly, 2's complement of 101100 is 010011 +1=010100.

| CHECK YOUR PROGRESS-IV                                                                                        |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 31. Computers use system where only two digits present.                                                       |  |  |  |  |  |

| 32. The octal numbers system has digits.                                                                      |  |  |  |  |  |

| 33. The hexadecimal numbers system has digits.                                                                |  |  |  |  |  |

| 34. Complements simplify the operation.                                                                       |  |  |  |  |  |

| State TRUE or FALSE:                                                                                          |  |  |  |  |  |

| 35. The decimal integer part is converted to r base by dividing it successively with r until it becomes zero. |  |  |  |  |  |

| 36. There are two types of complements present in r base system namely r's and $(r + 1)$ 's complement        |  |  |  |  |  |

| 37. 1's complement is obtained by just toggling all bits.                                                     |  |  |  |  |  |

| 38. The binary number system has base 2.                                                                      |  |  |  |  |  |

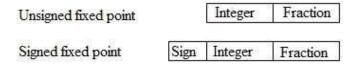

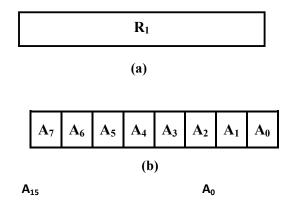

All positive integer numbers and zero can be considered as unsigned number. In order to represent negative numbers in computer signed numbers must be used. Because + and – signs are not present, rather these sign are represented by either '0' or '1'. The most significant bit of signed number is 0 for positive and 1 for negative. The fixed-point number representation has three parts as depicts in figure 1.6.

- Sign field

- Integer field

- Fractional field.

Figure 1.6: Fixed-point number representation

The 2's complementation representation is common in computer due to easier for arithmetic operations.

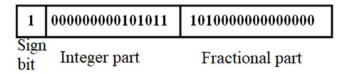

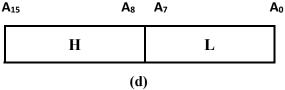

In a 32 bit register 1 bit reserved for the sign. Assume 15 bits are reserved for the integer part and 16 bits for the fractional part. The number -43.625 can be represented in register as depicted in figure 1.7.

Figure 1.7: Representation of -43.625

The sign bit 1 represent - and 00000000101011 is 15 bit binary equivalent for decimal 43 and 101000000000000 represent 16 bit binary equivalent for fraction 0.625.

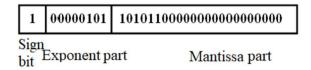

# 1.8.3 Floating-Point Representation

The floating number consists of two parts. The first part is a signed fixed point number that is called mantissa. The second part exponent represents the position of the decimal (or binary) point. The fixed

point mantissa is either fraction or integer. The floating point number always represent in the form  $Mx r^e$ .

n 0

Sign bit Exponent Mantissa

Figure 1.8: Floating point representation in register

The mantissa M and the exponent e present in the register with their sign as depicted in figure 1.8. A floating-point decimal number use base 10 for the exponent and binary number use base 2 for the exponent. A floating-point number is called normalized if the most significant bit (MSB) of the mantissa is 1. For positive integer, the MSB, or sign bit, is 0 and the remaining bits represent the magnitude. On the other hand for negative number, the MSB, or sign bit, is 1. The rest of the number can be represented in one of three ways

Signed-magnitude representation

Signed-1's complement representation

Signed-2's complement representation

Using floating point representation any non-zero number can be represented in the normalized form. Suppose, in 32-bit register 1 bit use as sign bit, 8 bits use for signed exponent, and remaining 23 bits represents fractional part. Now the decimal number -53.5 can represented as depicted in figure 1.9. The binary equivalent of -53.5 is (-110101.1)<sub>2</sub> and normalized representation is (-1.101011)x2<sup>5</sup>

Figure 1.9: Floating point representation of -53.5

# 1.8.4 Character Representation

Different character codes are used to represent alphanumeric characters in bits 0 and 1. The most commonly used character code is American standard Code for Information Interchange (ASCII).

**ASCII** uses 7-bits that provides 128 bit-patterns. In ASCII there are 26 lowercase and uppercase letters, 10 digits, and 32 punctuation marks. The remaining represents whitespace characters and special *control characters*. The uppercase A-Z, lowercase a-z and the digits 0-9 are in continuous series.

| Bit positions 654 |     |     |     |     |     |     |     | Bit positions |

|-------------------|-----|-----|-----|-----|-----|-----|-----|---------------|

| 000               | 001 | 010 | 011 | 100 | 101 | 110 | 111 | 3210          |

| NUL               | DLE | SP  | 0   | @   | Р   | ,   | р   | 0000          |

| SOH               | DC1 | !   | 1   | Α   | Q   | а   | q   | 0001          |

| STX               | DC2 | u   | 2   | В   | R   | b   | r   | 0010          |

| ETX               | DC3 | #   | 3   | С   | S   | С   | S   | 0011          |

| EOT               | DC4 | \$  | 4   | D   | Т   | d   | t   | 0100          |

| ENQ               | NAK | %   | 5   | E   | U   | е   | u   | 0101          |

| ACK               | SYN | &   | 6   | F   | V   | f   | v   | 0110          |

| BEL               | ETB | ,   | 7   | G   | W   | g   | w   | 0111          |

| BS                | CAN | (   | 8   | Н   | Х   | h   | х   | 1000          |

| HT                | EM  | )   | 9   | I   | Υ   | i   | У   | 1001          |

| LF                | SUB | *   | :   | J   | Z   | j   | z   | 1010          |

| VT                | ESC | +   | ;   | K   | [   | k   | {   | 1011          |

| FF                | FS  | ,   | <   | L   | \   | I   |     | 1100          |

| CR                | GS  | -   | =   | М   | ]   | m   | }   | 1101          |

| SO                | RS  |     | >   | N   | ۸   | n   | ~   | 1110          |

| SI                | US  | /   | ?   | 0   | _   | О   | DEL | 1111          |

### 1.9 SUMMING UP

- An instruction set is collection of machine language or assembly language instructions that are understood by central processing unit (CPU).

- The machine may be 3-address machines, 2-address machines, 1-address machines and 0-address machines

- The computer supported instructions types are Data Transfer Instructions, Arithmetic, Bit Manipulation, Program Execution Transfer, Processor Control, Iteration Control and Interrupt Instructions.

- The most commonly used addressing modes are Immediate, Direct, Indirect, Register, Register indirect, Displacement and Stack addressing.

- CPU or processor organization has three categories: Single Accumulator organization, General register organization and Stack organization.

- The register inside the processor is in top level memory hierarchy followed by cache memory and main memory respectively.

- The registers have two categories: user-visible registers and control and status registers

- **General-purpose registers** are used to store temporary data during execution of instruction.

- **Data registers** can be used to hold data only. It cannot be used for calculating of operand address.

- Address registers may either general purpose or devoted to an individual addressing mode.

- PC holds the address of the next instruction to be executed.

- IR holds the address of currently executed instruction.

- MAR holds the address of an instruction to be fetched.

- MBR holds data that needs the current instruction or the result produced by the instruction.

- The use of status flags:

**Sign:** It holds sign bit of the recent arithmetic operation. **Zero:** It is set when the result of operation is 0. **Carry:** It is set if addition operation produce a carry or borrow (for subtraction) from lower order bit.

- The numbers in computer are represented using binary number system.

- The floating number consists of two parts. The first part is a signed fixed point number that is called mantissa. The second part exponent represents the position of the decimal (or binary) point.

- In ASCII there are 26 lowercase and uppercase letters, 10 digits, and 32 punctuation marks. The remaining represents whitespace characters and special *control characters*.

# 1.10 ANSWERS TO CHECK YOUR PROGRESS

| 1. Register-register   | 20. False            |  |  |

|------------------------|----------------------|--|--|

| 2. Memory-memory       | 21. ALU              |  |  |

| 3. Destroyed           | 22. Three            |  |  |

| 4. Accumulator         | 23. hierarchy        |  |  |

| 5. Stack               | 24. General          |  |  |

| 6. True                | 25. Supervisor, user |  |  |

| 7. True                | 26. True             |  |  |

| 8. True                | 27. True             |  |  |

| 9. False               | 28. False            |  |  |

| 10. False              | 29. False            |  |  |

| 11. Memory location    | 30. True             |  |  |

| 12. Variable, constant | 31. Binary           |  |  |

| 13. Effective          | 32. Eight            |  |  |

| 14. Address            | 33. Sixteen          |  |  |

| 15. Register indirect  | 34. Subtraction      |  |  |

| 16. True               | 35. True             |  |  |

| 17. False              | 36. False            |  |  |

| 18. True               | 37. True             |  |  |

| 19. True               | 38. True             |  |  |

# 1.11 POSSIBLE QUESTIONS

#### **Short answer type questions:**

- 1. What is an instruction set?

- 2. Write the type of instruction for the following: JUMP, ADD

- 3. What are the types of CPU organization?

- 4. Arrange the followings in ascending order of access time: Secondary memory, Register, Main Memory, Cache Memory

- 5. What type of buses the system bus has?

- 6. What is the use of immediate addressing?

- 7. What is the Indirect Addressing? Give examples.

- 8. What is an accumulator?

- 9. Write assembly language code to evaluate X = (A-B) + (C-D) for stack based CPU

- 10. What are the categories of registers?

- 11. What happens to PC when interrupt occurs?

- 12. What is floating point representation?

- 13. What is 1's complement of 10011010?

- 14. What is 2's complement of 11000111?

- 15. Convert the decimal number 26.578 into binary number.

#### Long answer type questions:

- 1. Briefly explain the various addressing modes.

- 2. Briefly explain the instruction cycle.

- 3. List any five instruction types with adequate examples.

- 4. Convert decimal number 56.789 into binary, octal and hexadecimal number.

- 5. Briefly explain the data flow process with block diagram.

# 1.12 REFERENCES AND SUGGESTED READINGS

- Computer Architecture and Organization by B. Govindarajalu.; TMH publication.

- Advanced Computer Architecture A systems Design Approach by Richard Y. Kain; PHI Publication

- Computer Organization and Architecture Designing for Performance by William Stallings; Pearson Education

- Computer System Architecture by M. Morris Mano, PHI Publication.

# UNIT 2: COMBINATIONAL CIRCUITS AND ITS APPLICATIONS

#### Space for learners:

#### **Unit Structure**

- 2.1 Introduction

- 2.2Unit Objectives

- 2.3 AND-OR logic combinational circuit

- 2.4 AND-OR-Invert logic combinational circuit

- 2.5 Exclusive-OR logic

- 2.6 Exclusive-NOR logic

- 2.7 Implementing Combinational logic

- 2.7.1 Logic circuit design from boolean expression

- 2.7.2 Logic circuit design from truth table

- 2.8 The universal property of NAND and NOR gates

- 2.8.1 The NAND gate as a universal logic element

- 2.8.2 The NOR gate as a universal logic element

- 2.8.3 Combinational circuit using NAND gate

- 2.8.4 Combinational circuit using NOR gate

- 2.9 Combinational logic circuit Functionalities

- 2.9.1 The comparison function

- 2.9.2 The Arithmetic function

- 2.9.3 Basic Adders

- 2.9.3.1 The Half-Adder

- 2.9.3.2 The Full-Adder

- 2.9.3.3 Parallel Binary Adders

- 2.9.3.4 Truth table for 4-bit parallel adder

- 2.9.4 Binary Subtractor

- 2.9.4.1 The Half-Subtractor

- 2.9.4.2 The Full-Subtractor

- 2.9.5 Comparators

- 2.9.5.1 Equality

- 2.9.5.2 Inequality

- 2.9.6 Decoders

- 2.9.6.1 The Basic Binary Decoder

- 2.9.6.2 3-to-8 line Decoder

- 2.9.7 Encoders

- 2.9.7.1 Decimal to BCD Encoder

- 2.9.8 Multiplexers

- 2.9.9 Demultiplexers

- 2.10 Summing up

- 2.12 Answers to Check Your Progress

- 2.13 Possible Questions

- 2.14 References and Suggested Readings

#### 2.1 INTRODUCTION

This chapter describes the combinational circuits and the applications of combinational circuits. Sum of Product (SOP) and Product of Sum (POS) forms are the basic building blocks of the combinational circuits. When the logic gates are connected together to produce some specific output the resulting electronic circuit is known as combinational circuits. The output of the circuit always depends on the combination of the input variables.

#### 2.2UNIT OBJECTIVES

The unit is describing the designing and applications of combinational logic circuits. After completing the unit students' will able to:

- Analyze and apply different combinations of the logic gates.

- Design combinational circuits from the Boolean expressions.

- Design combinational circuits from the truth table.

- Describe the universal behaviour of NAND and NOR logic gates.

- Explain and describe adder circuits.

- Analyze the comparator circuits.

- Describe decoders and encoders

- Describe multiplexers and demultiplexers

#### 2.3 AND-OR LOGIC COMBINATIONAL CIRCUIT:

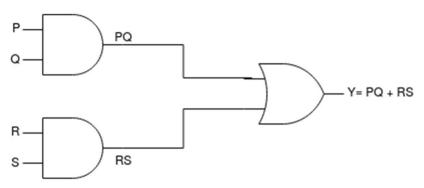

The Figure 2.1 shows an AND-OR circuit consisting of two input AND gates and one two input OR gate. The Boolean expression for the AND gate outputs and the resulting SOP expression for the

output Y are shown on the circuit diagram. The AND-OR circuit can have any number of AND and OR with any number of inputs.

Figure 2.1 AND-OR logic diagram

The truth table for the above combinational circuit is shown in Table-2.1. The outputs of the AND gates are also shown in the table.

|   | INP | UTS |   | PQ  | RS  | OUTPUT<br>Y |

|---|-----|-----|---|-----|-----|-------------|

| P | Q   | R   | S | 1.0 | INS |             |

| 0 | 0   | 0   | 0 | 0   | 0   | 0           |

| 0 | 0   | 0   | 1 | 0   | 0   | 0           |

| 0 | 0   | 1   | 0 | 0   | 0   | 0           |

| 0 | 0   | 1   | 1 | 0   | 1   | 1           |

| 0 | 1   | 0   | 0 | 0   | 0   | 0           |

| 0 | 1   | 0   | 1 | 0   | 0   | 0           |

| 0 | 1   | 1   | 0 | 0   | 0   | 0           |

| 0 | 1   | 1   | 1 | 0   | 1   | 1           |

| 1 | 0   | 0   | 0 | 0   | 0   | 0           |

| 1 | 0   | 0   | 1 | 0   | 0   | 0           |

| 1 | 0   | 1   | 0 | 0   | 0   | 0           |

| 1 | 0   | 1   | 1 | 0   | 1   | 1           |

| 1 | 1   | 0   | 0 | 1   | 0   | 1           |

| 1 | 1   | 0   | 1 | 1   | 0   | 1           |

| 1 | 1   | 1   | 0 | 1   | 0   | 1           |

| 1 | 1   | 1   | 1 | 1   | 1   | 1           |

Table 2.1 Truth table for the logic circuit of Figure 2.1

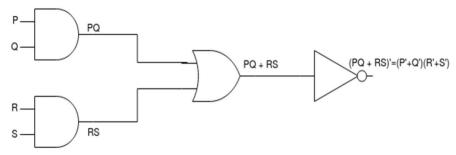

#### 2.4 AND-OR-INVERT LOGIC COMBINATIONAL CIRCUIT

If the output of the AND-OR circuit is complemented i.e. inverted, the resultant circuit is called AND-OR-Inverted circuit. The AND-OR logic implements the SOP expression and the corresponding

POS expressions can be obtained using the AND-OR-Inverted logic. The logic circuit diagram Figure 2.2 shows an AND-OR-Inverted circuit and development of the POS output expression.

$$Y = (P'+Q')(R'+S') = (PQ)'(RS)' = (((PQ)'(RS)')')' = (((PQ)')' + ((RS)'))')' = (PQ + RS)'$$

Figure 2.2 AND-OR Invert logic

In general, an AND-OR-Invert circuit can have any number of AND gates each with any number of inputs. A truth table can be developed from the AND-OR truth table in Table 2.1 by simply changing all 1s to 0s and all 0s to 1s in the output column.

#### **STOP TO CONSIDER**

- The AND-OR logic implements the SOP expressions, in other words, the SOP expressions are implemented using AND-OR logic.

- The AND-OR-Inverted logic implements POS expressions, in other words, the POS expressions are implemented using AND-OR-Inverted logic

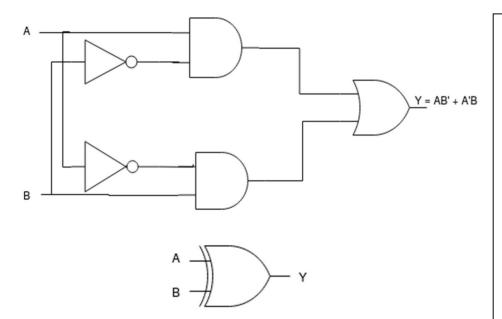

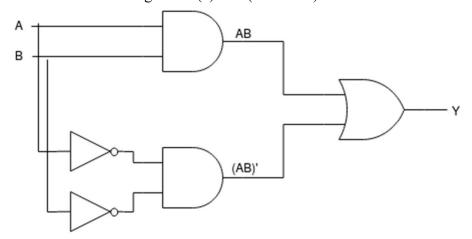

#### 2.5 EXCLUSIVE-OR LOGIC:

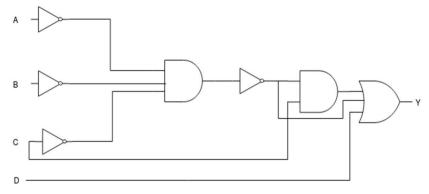

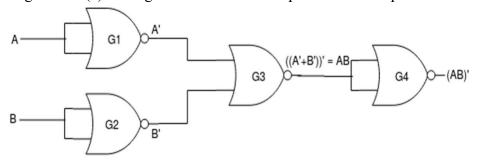

The exclusive-OR gate is considered a type of logic gate with its own unique symbol; it is actually a combination of two AND gates, one OR gate, and two inverters (NOT gate) as shown in Figure 2.3. The output is 1 only if the two inputs are at opposite levels.

Figure 2.3 Exclusive-OR logic

The output expression for the circuit in Figure 2.3 is Y = AB' + A'B i.e.  $Y = A \oplus B$

The truth table for exclusive-OR is shown in Table 2.2.

| A | В | Y |  |

|---|---|---|--|

| 0 | 0 | 0 |  |

| 0 | 1 | 1 |  |

| 1 | 0 | 1 |  |

| 1 | 1 | 0 |  |

Table 2.2: Truth table of exclusive-OR

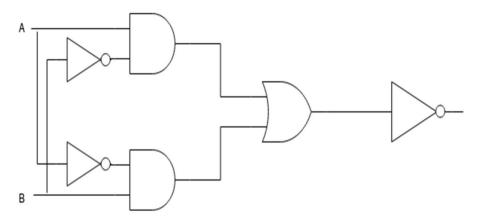

#### 2.6 EXCLUSIVE-NOR LOGIC

The complement of exclusive-OR is known as exclusive-NOR, which is derived as follows:

$$Y = (AB'+A'B)' = (AB')'(A'B)' = (A'+B)(A+B') = A'B' + AB$$

The output Y is 1 only if the two inputs A and B are at the same level. The exclusive-NOR can be implemented by simply inverting the output of an exclusive-OR. The following Figure 2.4 (a) shows

the exclusive-NOR and Figure 2.4(b) shows the direct implementation of the expression A'B'+AB.

#### Space for learners:

Figure 2.4(a) Y = (AB' + A'B)'

Figure 2.4(b) Y = A'B' + AB

#### STOP TO CONSIDER

- Exclusive-OR (XOR) logic is a combination of two AND gates, one OR gate, and two inverters (NOT gate)

- Exclusive-NOR (XNOR) logic is a combination of two AND gates, one OR gate, and three inverters (NOT gate) or XNOR is obtained by applying an inverter at the output of XOR.

#### **2.7 IMPLEMENTING COMBINATIONAL LOGIC**

This section will describe the methods of implementing the logic circuits. The first method describes the implementation from the Boolean expression and the second method describes the implementation from the truth table.

#### **Space for learners:**

#### 2.7.1 Logic circuit design from Boolean expression

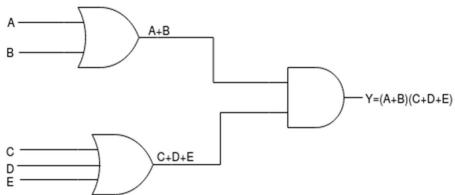

Let us consider the following Boolean expression:

$$Y = (A+B)(C+D+E)$$

A closer observation shows that the above expression 'Y' consists of two terms.

The first term is formed by doing OR operation between A and B, and the second term is formed by doing OR operation among C, D, and E. The two terms are then AND together to produce the final output Y. The OR operations must be performed before the AND operation.

To design the combinational circuit, a 2-input OR gate is required to form the term A+B and a 3-input OR gate is required to form the term C+D+E. A 2-input AND gate is then required to combine the two OR terms. The resulting logic circuit is shown in Figure 2.5.

Figure 2.5. Logic circuit for the expression Y = (A+B)(C+D+E)

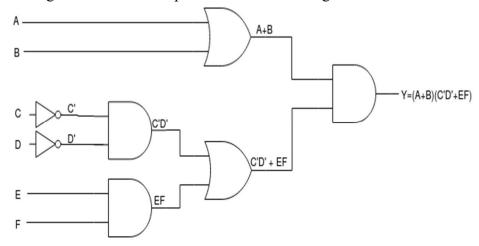

Let us implement the following expression as another example.

$$Y = (A+B)(C'D'+EF)$$

Like the previous example, let's have a closer look at the expression. The terms A+B and (C'D'+EF) are AND together to form Y. The term C'D'+EF is first formed by doing AND between C' and D', E and F and then performs OR operation between these two terms. Before getting the expression C'D' +EF, you must have the C'D' and EF, before these two terms you must have C' and D'. So, the logic operation must be performed in proper order. The logic gates

required to implement the expression Y = (A+B)(C'D'+EF) are as follows:

- a. Two NOT gates to get C' and D'

- b. Two 2-input AND gates to form C'D' and EF

- c. Two 2-input OR gates to form A+B and C'D'+EF

- d. One 2-input AND gate to form Y.

The logic circuit of this expression is shown in Figure 2.6

Figure 2.6. Logic diagram for the expression Y = (A+B)(C'D'+EF)

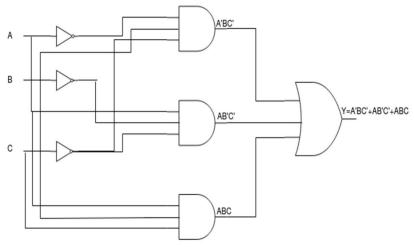

#### 2.7.2. Logic circuit design from truth table

Instead of using the SOP expression to design the combinational circuit you can use the truth table and from the truth table that you can derive using the SOP expression. Table 2.3 shows one example of such an implementation.

|   | Inputs |   | 1 - | <b>Product Terms</b> |

|---|--------|---|-----|----------------------|

| A | В      | C | Y   |                      |

| 0 | 0      | 0 | 0   |                      |

| 0 | 0      | 1 | 0   |                      |

| 0 | 1      | 0 | 1   | A'BC'                |

| 0 | 1      | 1 | 0   |                      |

| 1 | 0      | 0 | 1   | AB'C'                |

| 1 | 0      | 1 | 0   |                      |

| 1 | 1      | 0 | 0   |                      |

| 1 | 1      | 1 | 1   | ABC                  |

Table 2.3: Truth table for logic function

The Boolean expression obtained for the Table 2.3 is given below:

#### Y = A'BC' + AB'C' + ABC

The expression Y is obtained by doing OR operations among the product terms for which the output is 1. The first, second, and third are formed by doing AND operations among (A', B, C'), (A, B', C'), and (A, B, C) respectively. The logic gates required to implement the circuit are as follows:

- a. Three NOT gates.

- b. Three 3-input AND gates.

- c. One 3-input OR gate.

Figure 2.7 Logic diagram for the expression Y = A'BC'+AB'C'+ABC

Reduce the combinational logic circuit shown in Figure 2.8 to a minimum form.

Figure 2.8 Combinational logic circuit to be reduced

The expression for the output of the circuit is Y = (A'B'C')'C+(A'B'C')'+D

Applying D' Morgan's theorem and Boolean algebra,

$$Y = ((A')'+(B')'+(C')')C+(A')'+(B')'+(C')'+D$$

$$=$$

AC+BC+CC+A+B+C+D

$$=C(A+B+1)+A+B+C+D$$

$$Y=A+B+C+D$$

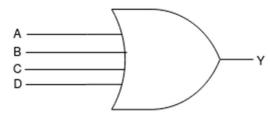

The simplified circuit is a 4-input OR gate as shown in the Figure 2.9

Figure 2.9 Reduced form the logic circuit of Figure 2.7

Note: Before implementing the logic circuit directly it is better to reduce the algebraic expressions to its minimized form so that the number of gates required to implement the circuit is minimum. This leads to reduction of propagation delay among the gates. More the number of gates, the more the propagation delay and also the heat produced by the circuit will increase.

#### STOP TO CONSIDER

- The implementation of combinational logic circuits is either from the Boolean expression or truth table.

- The expression should be carefully observed and has to identify the number of AND, OR, inverters required.

- Before implementing the logic circuit, it is advisable to reduce the expression by applying the boolean algebra

- If the number of gates are less in the final combinational circuit then the propagation delay will also be minimal.

#### **CHECK YOUR PROGRESS-I**

- 1. POS stands for \_\_\_

- 2. SOP stands for

- 3. An Exclusive-OR can be represented as

- 4. The number of AND gates required to implement the boolean expression ABC is \_\_\_\_\_

## 2.8 THE UNIVERSAL PROPERTY OF NAND AND NOR GATES

Till now, you have studied combinational circuits designing with AND and OR, and NOT gates. This section will describe the universal property of NAND and NOR gates. The universality of NAND means it can be used as an inverter and the combinations of NAND gates can be used to implement the AND, OR, and NOR operations. Similarly, the NOR gate can be used to implement the inverter, AND, OR, and NAND operations.

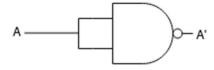

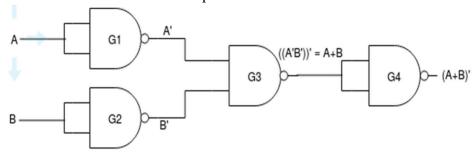

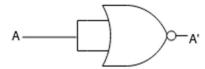

#### 2.8.1 The NAND gate as a universal logic element

The NAND gate is a universal gate because it can be used to produce the NOT, the AND, the OR, and the NOR functions. An inverter can be made from a NAND gate by connecting all of the inputs together and creating, in effect, a single input as shown in the Figure 2.10(a) for a 2-input gate. An AND function can be generated by the use of NAND gates alone as shown in Figure 2.10(b). An OR function can be implemented with only NAND gates, as shown in Figure 2.10(c). Similarly, the NOR function can also be produced as shown in Figure 2.10(d).

Figure 2.10(a) NAND gate as inverter or NOT

Figure 2.10(b) Two NAND gates are combined to produce AND operation

#

Figure 2.10(c) Three NAND gates are combined to produce OR operation

Figure 2.10(d) Four NAND gates are combine to produce NOR operation

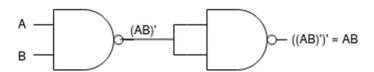

In Figure 2.10(b), a NAND gate is used to invert a NAND output to form the AND function which is given below:

$$Y = ((AB)')' = AB$$

In Figure 2.10(c), NAND gates G1 and G2 are combined to invert the two input variables before they are applied to NAND gate G3. The OR gate output is derived as follows by applying DeMorgans's theorem:

$$Y = ((A'B')' = A + B$$

In Figure 2.10(d), NAND gate G4 is used as an inverter connected to the circuit of part (c) to produce the NOR operation (A+B)'. Finally, we can conclude that using the NAND gate it is possible to implement any logic function.

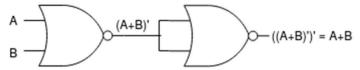

#### 2.8.2 The NOR gate as a Universal logic element

The NOR gate can also be used to produce the NOT, AND, OR, and NAND functions. A NOT circuit, or inverter, can be made from NOR gate by connecting all of the inputs together to effectively create a single input, as shown in Figure 2.11(a) with a 2-input example. Also, an OR gate can be produced from NOR gates as shown in Figure 2.11(b). An AND gate can be produced using the

NOR gates as shown in the Figure 2.11(c), the NOR gates G1 and G2 are used as inverters and the final output is derived by the use of DeMorgan's theorem as follows:

$$Y = (A' + B')' = AB$$

Figure 2.11(d) shows the implementation of NAND function using NOR gates. Hence we can conclude that the NOR gate can also work as a universal gate like the NAND gate.

Figure 2.11(a) NOR gate used as inverter

Figure 2.11(b) NOR gates are combined to produce OR operation

Figure 2.11(c) NOR gates are combined to produce AND operation

Figure 2.11(d) NOR gates are combined to produce NAND operation

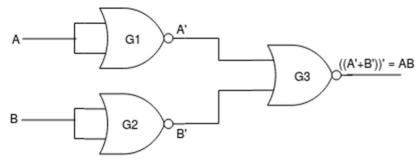

#### 2.8.3 Combinational circuit using NAND gate

NAND gates can work as either NAND or negative OR by applying DeMorgan's theorem.

$$(AB)' = A' + B'$$

Consider the NAND logic as shown in Figure 2.12. The output expression is developed in the following steps:

# Y = ((AB)' (CD)')'= ((A'+B')(C'+D'))'= (A'+B')'+(C'+D')'= (A')'(B')' + (C')'(D')'= AB + CDA G1 G3 O-Y=AB+CD

Figure 2.12 Implementation of the Boolean expression Y= AB+CD using NAND gate

#### 2.8.4 Combinational circuit using NOR gate

The NOR gate can work as either a NOR or negative AND, as shown by DeMorgan's theorem.

$$(A+B)' = A'B'$$

Consider the NOR logic in Figure 2.13. The output expression is developed as follows:

$$Y = ((A+B)'+(C+D)')' = ((A+B)')'((C+D)')' = (A+B)(C+D)$$

A

B

G1

G3

G2

G4+B)'

G3

G4+B)(C+D)

Figure 2.13 Implementation of the boolean expression Y= (A+B)(C+D) using NOR gate

#### STOP TO CONSIDER

- NAND and NOR gates are called universal gates.

- NAND and NOR can be used to implement all the primary logic like AND, OR, NOT(invert).

- NAND can produce NOR and, similarly, NOR can produce NAND.

#### **CHECK YOUR PROGRESS-II**

- 5. The number of NOR gate(s) required to implement OR is/are

- 6. The number of NAND gates(s) required to implement AND is/are

- 7. The number of NAND gates(s) required to implement Y = A'+B is/are

- 8. The number of NOR gates(s) required to implement Y = A'+B is/are

# 2.9 COMBINATIONAL LOGIC CIRCUIT FUNCTIONALITIES

In this section, many types of fixed functions of combinational circuits are introduced, viz. Adders, comparator, decoders, encoders, code converters, multiplexer, demultiplexer etc.

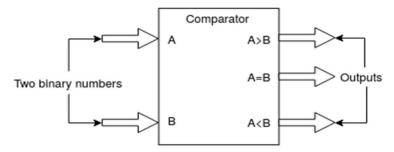

#### 2.9.1 The comparison function

The magnitude of comparison performed by a logic circuit is called a comparator. A comparison compares two quantities and indices whether or not they are equal. Figure 2.14 represents a comparison function, one number in binary form is applied to input A, and the other number in binary form is applied to input B. The outputs indicate the relationship of the two numbers by producing 1 on the proper output line. Suppose that the binary representation of 3 is applied to input A and a binary representation of the number 6 is applied to input B. A '1' (HIGH) will appear on the A<B output, indicating the relationship between the two numbers.

Figure 2.14 Basic magnitude comparator

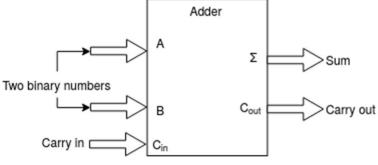

#### 2.9.2 The Arithmetic functions

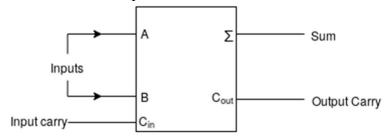

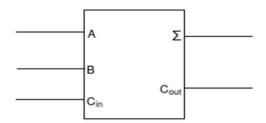

**Addition** is performed by a logic circuit called adder. An adder adds two binary numbers on inputs A and B with a carry input  $(C_{in})$  and generates a sum  $(\Sigma)$  and a carry output  $(C_{out})$  as shown in Figure 2.15.

Figure 2.15 Basic Adder

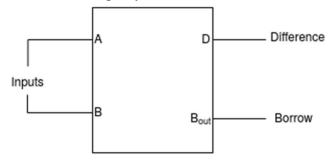

**Subtraction** is also performed by a logic circuit. A subtractor requires three inputs, viz.,the two numbers that are to be subtracted and a borrow input. The two outputs are the difference and the borrow output. The subtraction operation is a special case of addition operation.

**Multiplication:** A multiplier is a logic circuit that performs multiplication. Because numbers are always multiplied in twos, two inputs are necessary. The product is the multiplier's output. Multiplication can be achieved using an adder in conjunction with other circuits since it is merely a series of additions with shifts in the positions of the partial products.

**Division:** Division can be achieved with a series of subtraction, comparisons, and shifts, therefore an adder can be used in conjunction with other circuits. The division requires two inputs, and the quotient and remainder are generated as outputs.

Code conversion: The logic circuits can also be used for code conversion. A code is a collection of bits arranged in a specific pattern and used to represent data. A code converter converts one type of coded data into another type of coded data. For example, Conversion from binary to Binary Coded Decimal (BCD) or Gray code.

**Encoder:** The **encoder** is a logic circuit that performs the encoding function. The encoder turns data into a coded representation, such as

a decimal number or an alphanumeric letter. One form of encoder, for example, turns all of the decimal digits, 0 through 9, to binary code.

Space for learners:

**Decoder:** A logic circuit called a *decoder* performs the decoding operation. The decoder translates coded data, such as binary numbers, to uncoded data, such as decimal numbers. One form of decoder, for example, translates a 4-bit binary code into the appropriate decimal digits.

Data selection function: The multiplexer and the demultiplexer are two types of circuits that select data in the data selection function. A multiplexer, often known as a MUX, is a logic circuit that transfers digital data from many input lines to a single output line in a predetermined time sequence. A multiplexer can be thought of as an electronic switch that links each of the input lines to the output line in a sequential manner. A demultiplexer (DEMUX) is a logic circuit that converts digital data from one input line to multiple output lines in a predetermined order. The demux is a reverse mux. When data from numerous sources needs to be sent across one line to a distant place and then redistributed to multiple recipients, multiplexing and demultiplexing are utilized.

#### **STOP TO CONSIDER**

• The AND, OR, and NOT can be used to design the complex logic circuits to perform specific operations.

#### 2.9.3 Basic Adders

Adders are essential not only in computers, but also in a wide range of digital systems that process numerical data. The study of digital systems requires a basic understanding of the adder action. The half-adder and full-adder are described in this section.

#### 2.9.3.1 The Half-Adder

Recall the basic rules for binary addition

0+0 = 0

0+1=0

$$1+0 = 1$$

$1+1 = 10$

A logic circuit known as a half-adder performs the operations.

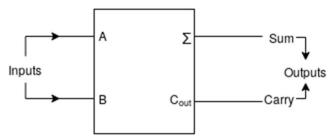

The half-adder takes two binary digits as inputs and produces two binary digits, a sum bit and a carry bit, as outputs. Figure 2.16 shows a half-adder represented by the logic symbol.

Figure 2.16 Logic symbol for a half-adder

*Half-Adder Logic* from the operation of the half-adder as stated in Table 2.3, expressions can be derived for the sum and the output carry as functions of the inputs. Note that the output carry ( $C_{out}$ ) is a 1 only when both A and B are 1s, therefore,  $C_{out}$  can be expressed as the AND of the input variables.  $C_{out} = AB$ .

Table 2.3 Half-adder truth table

| A | В | Cout | Σ |

|---|---|------|---|

| 0 | 0 | 0    | 0 |

| 0 | 1 | 0    | 1 |

| 1 | 0 | 0    | 1 |

| 1 | 1 | 1    | 0 |

Now, observe that the sum  $(\Sigma)$  is a 1 only if the input variables, A and B, are not equal. The sum can therefore be expressed as the exclusive-OR of the input variables.  $\Sigma = A \oplus B$ . The logic implementation required for the half-adder function can be developed using  $\Sigma$  and  $C_{out}$ . The output carry is produced with AND gate with A and B on the inputs, and the sum output is generated with an exclusive-OR (XOR) gate, as shown in Figure 2.17. Remember, the XOR is implemented with AND gates, an OR gate, and inverters.

Figure 2.17 Half-adder logic diagram

#### 2.9.3.2 The Full Adder

The second category of adder is the full-adder. The full-adder accepts two input bits and an input carry and generates a sum output and an output carry. The basic difference between full-adder and a half-adder is that the full-adder accepts an input carry. A logic symbol for a full-adder is shown in Figure 2.18, and the truth table in Table 2.4 shows the operation of a full-adder.

Figure 2.18 Logic symbol for a full-adder

| Table 2.41 all adder tratif table |   |     |      |   |  |  |  |  |

|-----------------------------------|---|-----|------|---|--|--|--|--|

| A                                 | В | Cin | Cout | Σ |  |  |  |  |

| 0                                 | 0 | 0   | 0    | 0 |  |  |  |  |

| 0                                 | 0 | 1   | 0    | 1 |  |  |  |  |

| 0                                 | 1 | 0   | 0    | 1 |  |  |  |  |

| 0                                 | 1 | 1   | 1    | 0 |  |  |  |  |

| 1                                 | 0 | 0   | 0    | 1 |  |  |  |  |

| 1                                 | 0 | 1   | 1    | 0 |  |  |  |  |

| 1                                 | 1 | 0   | 1    | 0 |  |  |  |  |

| 1                                 | 1 | 1   | 1    | 1 |  |  |  |  |

Table 2.4 Full-adder truth table

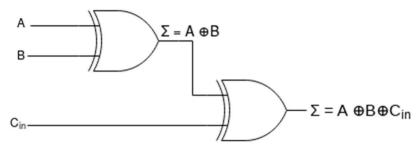

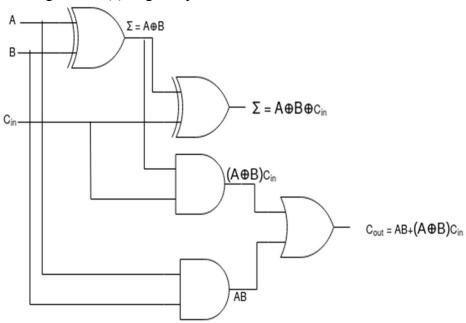

**Full-Adder Logic** The full-adder must add the two input bits and input carry. From the half-adder you know that the sum of the input bits A and B is exclusive-OR of those variables.  $A \oplus B$ . For the input carry  $(C_{in})$  to be added to the input bits, it must be exclusive-ORed with  $A \oplus B$ , yielding the equation for the sum output of the full-adder.

$\Sigma = (A \bigoplus B) \bigoplus C_{in}$ . This means that to implement the full-adder sum function, two 2-input exclusive-OR gates can be used. The first must generate the term  $A \bigoplus B$ , and the second has as its inputs the output of the first XOR gate and the input carry, as shown in Figure 2.19(a).

Figure 2.19(a) Logic required to form the sum of three bits

Figure 2.19(b) Complete logic circuit for a full-adder

The output carry is a 1 when both inputs to the first XOR gate are 1s or when both inputs to the second XOR gate are 1s. You can verify this fact by studying Table 2.4. The output carry of full-adder is therefore produced by the inputs A ANDed with B and  $A \oplus B$

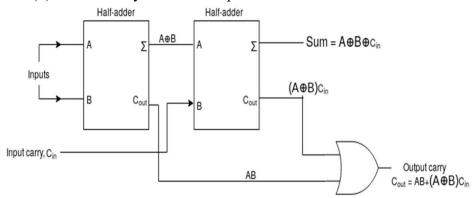

ANDed with C<sub>in</sub>. These two terms are ORed, as expressed in the expression of C<sub>out</sub>. This function is implemented and combined with the sum logic to form a complete full-adder circuit, as shown in Figure 2.19(b). Notice that in Figure 2.19(b) there are two half-adders, connected as shown in the block diagram of Figure 2.20(a), with their output carries ORed. The logic symbol shown in Figure 2.20(b) will normally be used to represent the full-adder.

Figure 2.20(a) Arrangement of two half-adders to form a full-adder

Figure 2.20(b) Full-adder logic symbol

#### 2.9.3.3 Parallel Binary Adders

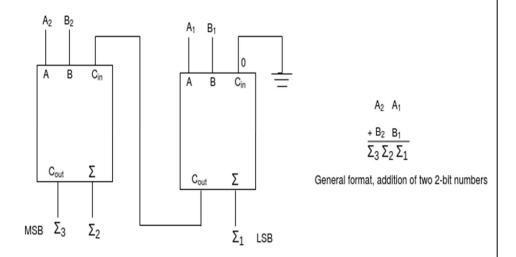

Parallel binary adders are formed by connecting two or more full-adders. The basic operations of such adders, as well as their associated input and output functions, are described in this section. A single full-adder can add two one-bit numbers as well as an input carry. Additional full-adders must be used to add binary numbers with more than one bit. As shown above with 2-bit integers, when one binary number is added to another, each column creates a sum bit and a 1 or 0 carry bit to the next column to the left.

In this case, the second column's carry bit becomes the third column's sum bit. A full adder is required for each bit in two binary numbers to be added. So two adders are required for 2-bit numbers, four adders are required for 4-bit values, and so on. Each adder's carry output is connected to the next higher-order adder's carry input, as shown in Figure 2.21 for a 2-bit adder. Because there is no carry input to the least significant bit location, either a half-adder or the carry input of a full-adder can be set to 0 (grounded). In Figure 2.21 the least significant bits (LSB) of the two numbers are represented by  $A_1$  and  $B_1$ . The next higher-order bits are represented by  $A_2$  and  $B_2$ . The three sum bits are  $\Sigma_1$ ,  $\Sigma_2$ , and  $\Sigma_3$ . Notice that the output carry from the left-most full-adder becomes the most significant bit (MSB) in the sum  $\Sigma_3$ .

Fig 2.21. A 2-bit adder

#### **Four-bit Parallel Adders**

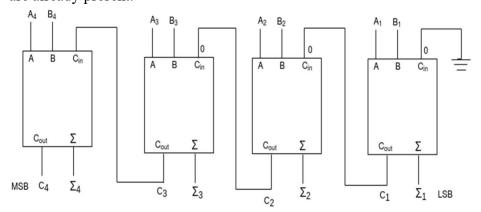

A nibble is a collection of four bits. As demonstrated in Figure 2.22, a basic 4-bit parallel adder is developed with four full-adder stages. The LSBs (A<sub>1</sub> and B<sub>1</sub>) of each number being added are applied to the right-most full-adder; the higher-order bits are applied to the gradually higher-adders as illustrated; and the MSBs (A<sub>4</sub> and B<sub>4</sub>) of each number are applied to the left-most full-adder. The carry output of each adder is connected to the carry input of the next higher-order adder as indicated. These are called internal carries.

In terms of the method used to handle carries in a parallel adder, there are two types: the *ripple carry* adder and *carry look-ahead* adder. A *ripple carry* adder is one in which the carry output of each full-adder is connected to the carry input of the next higher-order stage (a stage is one full-adder). The sum and the output carry of any stage cannot be produced until the input carry occurs. This causes a time delay in the addition process. The carry propagation delay for each full-adder is the time from the application of the input carry until the output carry occurs, assuming that the A and B inputs are already present.

Figure 2.22 A 4-bit Adders

Look-ahead carry addition is a technique for speeding up the addition process by eliminating the *ripple carry* delay. The *look-ahead carry* adder predicts each stage's output carry and produces it using either *carry generation* or *carry propagation* based on the input bits of each stage.

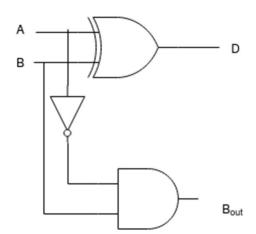

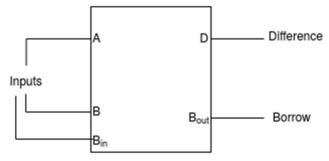

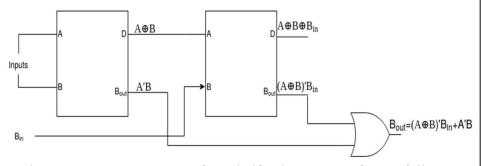

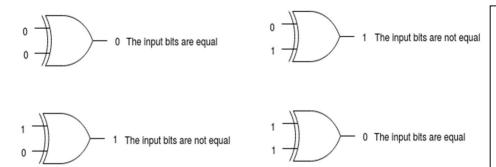

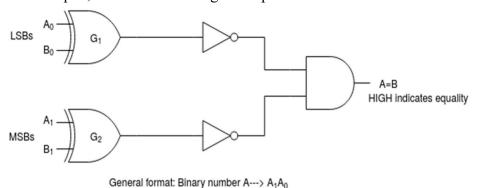

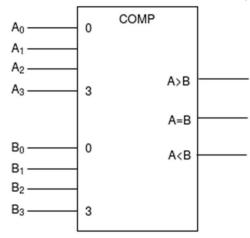

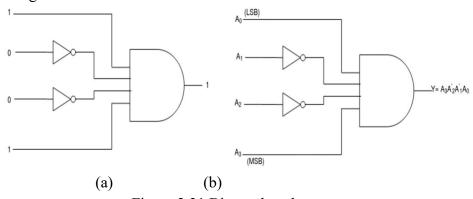

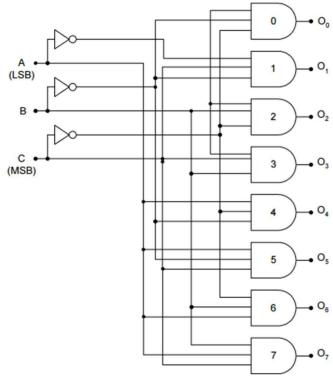

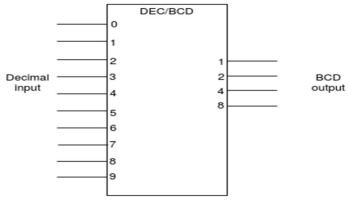

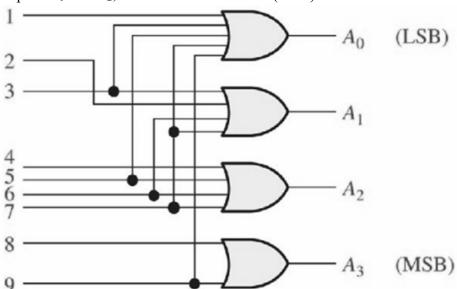

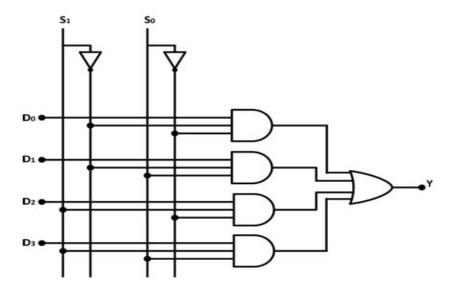

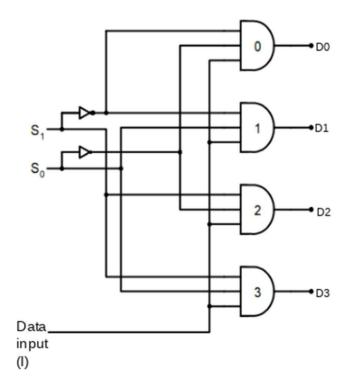

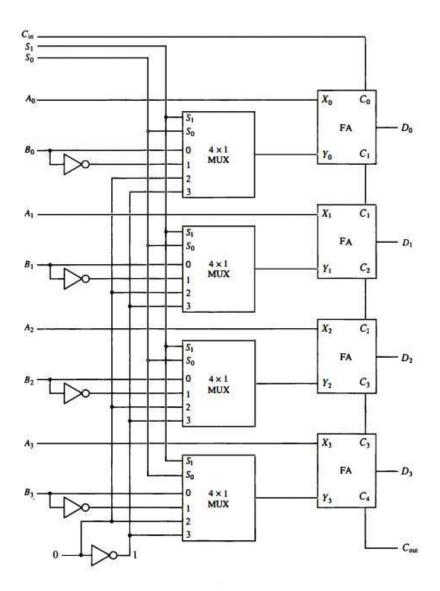

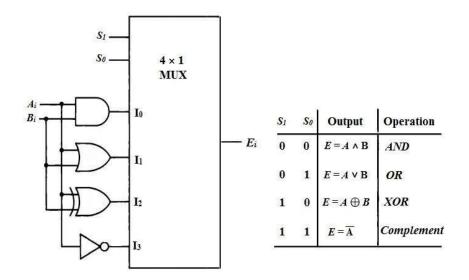

Carry generation occurs when an output carry is produced (generated) internally by the full-adder. A carry is generated only when both input bits are 1s. The generated carry,  $C_g$ , is expressed as the AND function of the two input bits, A and B.  $C_g$ =AB.